https://elpais.com/tecnologia/2016/10/19/actualidad/1476873307_047514.html

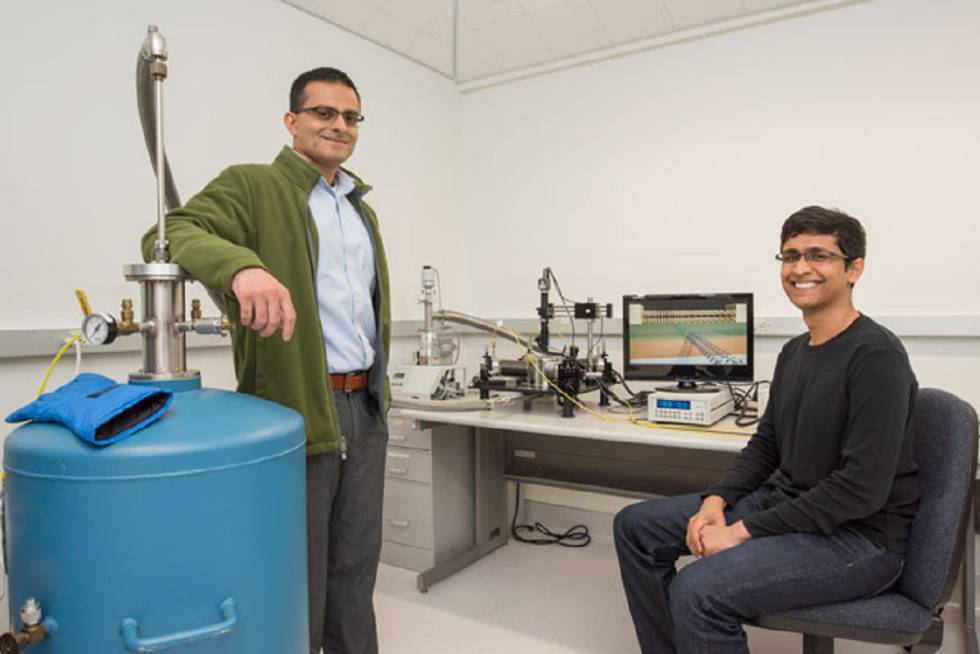

Ampliar fotoEl profesor Ali Javey y el graduado Sujay Desai en el Berkeley Lab junto a sus instrumentos para el análisis de los transistores de 1 nm. MARILYN CHUNG/BERKELEY LA

Ampliar fotoEl profesor Ali Javey y el graduado Sujay Desai en el Berkeley Lab junto a sus instrumentos para el análisis de los transistores de 1 nm. MARILYN CHUNG/BERKELEY LA

Investigadores del Lawrence Berkeley National Laboratory de Berkeley (Estados Unidos) han fabricado un transistor de 1 nanómetro, llevando más allá una de las limitaciones físicas que las escalas tan reducidas imponen a los microchips actuales. Para conseguirlo han utilizado nanotubos de carbono y un material llamado disulfuro de molibdeno sobre la capa de silicio convencional.

La física impone un límite a la carrera sin fin por la miniaturización de los componentes básicos de la microelectrónica, límite al que siempre parece que nos estamos aproximando. La regla general es que cuanto más pequeños son los transistores de un chip, mejor: eso permite crear procesadores más rápidos, con menor consumo y de tamaño más reducido (o con más transistores en el mismo espacio). Ahí es donde entran los límites de la física: a partir de ciertos tamaños se sabe que los efectos cuánticos en los átomos de que están compuestos esos transistores harán inviable su funcionamiento.

Los expertos utilizan varias escalas clave en la fabricación de los transistores de los microchips, que hoy en día rondan los 14 nm (nanómetros, millonésimas de milímetro), aunque los de 22 y 32 nm también son muy comunes. Los transistores de Intel en los chips de la familia Broadwell, Atom y Skylake son de 14 nm; algo similar sucede en los de Apple: los A9 y A10 son de 14 y 16 nm, fabricados por Samsung y TSMC. El siguiente salto tecnológico son los 10 nm (previstos para 2017) para pasar luego a los 5 nm hacia 2020. Pero estas aspiraciones de futuro son, de momento, meras conjeturas.

NEC e IBM ya fabricaron en 2002 y 2003 transistores de 5 y 6 mm a modo de demostración, y, posteriormente, otros de 10 nm con buen rendimiento, dando una pista acerca de que los nanotubos de carbono podrían ser el camino. Esto ha sido confirmado con la fabricación de demostración del transistor más pequeño del mundo, de tan solo 1 nm, en el Berkeley Lab. El trabajo completo con todos los detalles ya se ha publicado en la revista Science.

Nuevos materiales para una nueva escala

El disulfuro de molibdeno que se ha utilizado reemplaza al silicio como componente de las puertas del transistor. Tiene propiedades interesantes, según sus creadores, especialmente su buen comportamiento eléctrico. Esto permite encenderlo y apagarlo millones de veces por segundo, como los transistores actuales de los microchips. El nanotubo de carbono se emplea durante su fabricación porque los sistemas convencionales, como la litografía, no sirven a esa escala. Además, se aprovecha su estructura cilíndrica a modo de electrodos, con buen comportamiento.

El avance que supone este transistor es interesante, pero los investigadores avisan de que se trata tan solo de una demostración científica, como las que ya hicieran IBM, NEC, Toshiba y otros hace más de una década: “Es una prueba de concepto. Ni hemos empaquetado miles de millones de transistores en un chip ni hemos desarrollado los sistemas para evitar las complicaciones típicas que surgen durante el proceso de fabricación. Pero es importante haber demostrado que ya no estamos limitados a 5 nm con el tamaño de las puertas de los transistores. La Ley de Moore podrá seguir cumpliéndose si somos capaces de utilizar los materiales, arquitectura e ingenierías adecuadas”, advierten.

En 1965, uno de los fundadores de Intel, Gordon Moore, afirmó que el número de transistores en un chip se duplicaría "cada dos años”. Con el tiempo, un profesor del Cal Tech le otorgó el sobrenombre de Ley de Moore y el término cuajó. Luego sufriría ligeras modificaciones, incluyendo referencias a “la capacidad de procesamiento del chip” y al “tamaño de los transistores”. Incluso en vez de dos años se refinó el periodo de duplicación a 18 meses y se incluyeron factores como que “el coste se reducirá a la mitad”. El caso es que la definición es muy laxa y a raíz de esto surgieron todo tipo de controversias, la más común sobre dónde estaba el límite a la famosa Ley.

Entendidas literalmente, algunas de las acepciones de la Ley de Moore parecen tener un límite lógico y físico: el tamaño de los átomos. Es por ello que cuando se entra en la escala de los nanómetros el asunto se complica: si un transistor mide más o menos 1 nanómetro es tan solo diez veces más grande que los 0,1 nanómetros que mide la «nube de electrones» de un átomo típico – y es difícil fabricar algo más pequeño. Los chips actuales tienen transistores de entre 10 y 20 nm y son tan solo 100 o 200 veces más grandes que esos átomos. Sin embargo, ingenieros y científicos siguen trabajando en hacer que la Ley de Moore perdure, con ingenio y nuevos descubrimientos que –de momento– van salvando la afirmación de Moore.

No hay comentarios:

Publicar un comentario